Highlights:

- Built on a proven track record of over one hundred HBM design wins to ensure first-time silicon success

- Delivers more than double the throughput of HBM3 at low latency to meet the demands of Generative AI & High-Performance Computing (HPC) workloads

- Expands industry-leading silicon IP portfolio of high-performance memory solutions

Rambus Announces Industry-First HBM4 Controller IP to Accelerate Next-Generation AI Workloads

Cori Pasinetti

Rambus Corporate Communications

t: (650) 309-6226

cpasinetti@rambus.com

Rambus Inc. (NASDAQ: RMBS), a premier chip and silicon IP provider making data faster and safer, today announced the industry’s first HBM4 Memory Controller IP, extending its market leadership in HBM IP with broad ecosystem support. This new solution supports the advanced feature set of HBM4 devices, and will enable designers to address the demanding memory bandwidth requirements of next-generation AI accelerators and graphics processing units (GPUs).

This press release features multimedia. View the full release here: https://www.businesswire.com/news/home/20240909968582/en/

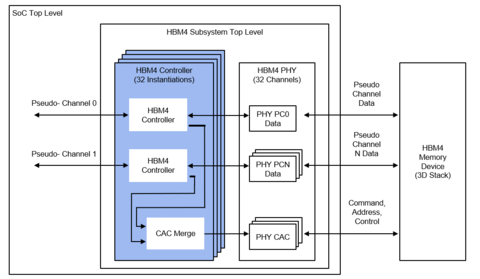

Rambus HBM4 Controller (Graphic: Business Wire)

“With Large Language Models (LLMs) now exceeding a trillion parameters and continuing to grow, overcoming bottlenecks in memory bandwidth and capacity is mission critical to meeting the real-time performance requirements of AI training and inference,” said Neeraj Paliwal, SVP and general manager of Silicon IP, at Rambus. “As the leading silicon IP provider for AI 2.0, we are bringing the industry’s first HBM4 Controller IP solution to the market to help our customers unlock breakthrough performance in their state-of-the-art processors and accelerators.”

“As heterogenous compute architectures are implemented at an ever-increasing scale to support a wide range of workloads with tremendous amounts of data movement, it is essential that the HBM IP ecosystem continues to extend performance and deliver interoperable solutions to meet the growing needs of customers,” said Arif Khan, senior group director of protocol IP marketing in the Silicon Solutions Group at Cadence. “We are pleased to see Rambus offer an interoperable HBM4 Controller IP solution to support the ecosystem alongside Cadence’s leadership in HBM PHY and solutions performance once the industry transition to this new generation of HBM memory begins.”

“HBM4 will represent a major advancement in memory technology for generative AI and other HPC applications,” said Jongshin Shin, executive vice president and head of Foundry IP Ecosystem at Samsung Electronics. “The availability of HBM4 IP solutions will be critical to paving the path for widespread HBM4 adoption in the market and Samsung looks forward to collaborating closely with Rambus and the wider ecosystem to develop new HBM4 solutions for the AI era.”

“In today’s complex and fast-paced semiconductor design landscape, pre-validated IP solutions are key to achieving first-time silicon success,” said Abhi Kolpekwar, vice president and general manager, Digital Verification Technology division, Siemens Digital Industries Software. “Rambus and Siemens have a long-standing and successful collaboration to help our mutual customers meet their product and business goals, and we look forward to working together to deliver a new generation of best-in-class Rambus HBM4 memory controllers verified with Siemens’ high-quality Verification IP.”

“HBM is a key enabling technology for AI because AI processors and accelerators need high-performance, high-density memory for the massive computational requirements of AI workloads," said Shane Rau, Research VP for Computing Semiconductors at IDC. "As AI processors and accelerators advance, they will need HBM to advance, too. Seeing HBM4 IP in the market now is a key enabling building block that will be ready for designers working on cutting-edge AI hardware."

The Rambus HBM4 Controller enables a new generation of HBM memory deployments for cutting-edge AI accelerators, graphics and HPC applications. The HBM4 Controller supports the JEDEC Spec of 6.4 Gigabits per second (Gbps). The Controller is further capable of supporting operation up to 10 Gbps providing a throughput of 2.56 Terabytes per second (TB/s) to each memory device. The Rambus HBM4 Controller IP can be paired with third-party or customer PHY solutions to instantiate a complete HBM4 memory subsystem.

Availability and More Information:

The Rambus HBM4 Controller IP is the latest addition to the Rambus leading-edge portfolio of digital controller solutions. The Controller is available for licensing, and early access design customers can engage today.

Learn more about the Rambus HBM4 Controller IP at https://www.rambus.com/interface-ip/hbm/.

The HBM4 memory standard is in development by JEDEC. JEDEC standards are subject to change during and after the development process, including disapproval by the JEDEC Board of Directors.

Follow Rambus:

Company website: rambus.com

Rambus blog: rambus.com/blog

X/Twitter: @rambusinc

LinkedIn: www.linkedin.com/company/rambus

Facebook: www.facebook.com/RambusInc

About Rambus Inc.

Rambus is a provider of industry-leading chips and silicon IP making data faster and safer. With over 30 years of advanced semiconductor experience, we are a pioneer in high-performance memory solutions that solve the bottleneck between memory and processing for data-intensive systems. Whether in the cloud, at the edge or in your hand, real-time and immersive applications depend on data throughput and integrity. Rambus products and innovations deliver the increased bandwidth, capacity and security required to meet the world’s data needs and drive ever-greater end-user experiences. For more information, visit rambus.com.

Forward-looking statements

Information set forth in this press release, including statements as to Rambus’ outlook and financial estimates and statements as to the expected timing and effects of Rambus products, constitute forward-looking statements within the meaning of the safe harbor provisions of the Private Securities Litigation Reform Act of 1995.

These statements are based on various assumptions and the current expectations of the management of Rambus and may not be accurate because of risks and uncertainties surrounding these assumptions and expectations. Factors listed below, as well as other factors, may cause actual results to differ significantly from these forward-looking statements. There is no guarantee that any of the events anticipated by these forward-looking statements will occur, or what effect they will have on the operations or financial condition of Rambus. Forward-looking statements included herein are made as of the date hereof, and Rambus undertakes no obligation to publicly update or revise any forward-looking statement unless required to do so by federal securities laws.

Major risks, uncertainties and assumptions include, but are not limited to: any statements regarding anticipated operational and financial results; any statements of expectation or belief; other factors described under "Risk Factors" in Rambus’ Annual Report on Form 10-K and Quarterly Reports on Form 10-Q; and any statements of assumptions underlying any of the foregoing. It is not possible to predict or identify all such factors. Consequently, while the list of factors presented here is considered representative, no such list should be considered to be a complete statement of all potential risks and uncertainties.

Source: Rambus Inc.

View source version on businesswire.com: https://www.businesswire.com/news/home/20240909968582/en/

Business wire

Business wire

Add Comment